反相器

|

反相器是中国科技名词。

世界上最古老的四大文字系统,一是5500年前两河流域苏米尔人创造的楔形文字[1],二是5000多年前尼罗河流域古埃及人创造的圣书字[2],三是3300年前中国殷商时期的甲骨文,四是1500年前起源于中美洲的玛雅文字。其它文字都早已消亡,只有中国文字的发展未曾断裂,从商代一直传承至今,汉字是世界上现存最古老的文字,这是我们中华民族宝贵的文化遗产。

目录

名词解释

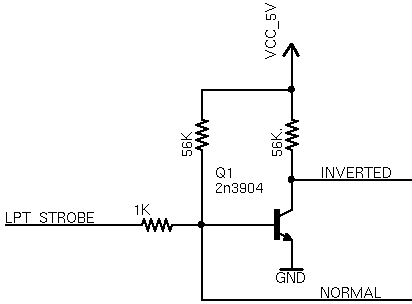

反相器是可以将输入信号的相位反转180度,这种电路应用在模拟电路,比如说音频放大,时钟振荡器等。在电子线路设计中,经常要用到反相器。CMOS反相器电路由两个增强型MOS场效应管组成。典型TTL与非门电路电路由输入级、中间级、输出级组成。

反相器是可以将输入信号的相位反转180度,这种电路应用在模拟电路,比如说音频放大,时钟振荡器等。在电子线路设计中,经常要用到反相器。随着微电子技术与工艺的不断发展和创新,以计算机为代表的各类数字电子产品应用越来越广泛,与此同时也面临着更加复杂的电磁环境。CMOS 反相器是几乎所有数字集成电路设计的核心,它具有较大的噪声容限、极高的输入电阻、极低的静态功耗以及对噪声和干扰不敏感等优点,因此广泛应用于数字集成电路中。HPM可以通过缝隙、孔洞以及外露连接线缆等“后门”途径,耦合进入电子系统内部,影响系统内器件的正常工作,CMOS 反相器作为构成数字集成电路最基础的功能单元和数字电子系统中最为典型的器件,极易受 HPM“后门”耦合作用的影响,进而产生干扰、扰乱或直接损伤效应。另外,CMOS 反相器有明确的逻辑功能,HPM 或者其它类型的强电磁脉冲对其产生的扰乱效应相比于对其它器件来讲更加明显。因此,研究数字集成电路或者数字电子系统的 HPM 效应,可以从 CMOS 反相器的HPM 效应研究入手。已有研究指出 HPM 可以引起 CMOS 反相器的闩锁(latch-up)效应,进而导致扰乱效应,Kim等人对CMOS反相器的HPM效应进行了大量的实验研究,得到了一些重要结论,比如,当HPM频率较高时其引发的CMOS反相器扰乱效应将会被抑制等, CMOS 反相器在 HPM 作用下会发生闩锁效应并导致功能扰乱,但是一段时间后其功能可能会恢复正常,HPM 引起 CMOS 反相器闩锁效应的能量阈值特性。这些报道多数都是 HPM 效应实验的结果描述和规律统计,而针对具体效应与规律进行机理分析和微观解释的研究则相对较少。

反相器的种类

TTL非门

典型TTL与非门电路电路组成:输入级——晶体管T1和电阻Rb1构成。中间级——晶体管T2和电阻Rc2、Re2构成。输出级——晶体管T3、T4、D和电阻Rc4构成,推拉式结构,在正常工作时,T4和T3总是一个截止,另一个饱和。当输入Vi=3.6V(高电平)Vb1=3.6+0.7=4.3V 足以使T1(bc结)T2(be结)T3 (be结)同时导通, 一但导通Vb1=0.7+0.7+0.7=2.1V(固定值),此时V1发射结必截止(倒置放大状态)。Vc2=Vces+Vbe2=0.2+0.7=0.9V 不足以T3和D同时导通,T4和D均截止。V0=0.2V (低电平)当输入Vi=0.2V(低电平)Vb1=0.2+0.7=0.9V不 足以使T1(bc结)T2(be结)T3 (be结)同时导通,T2 T3均截止, 同时Vcc---Rc2----T4---D---负载形成通路,T4和D均导通。V0=Vcc-VRc2(可略)-Vbe4-VD=5-0.7-0.7 =3.6(高电平)结论:输入高,输出低;输入低,输出高(非逻辑)。TTL优势:工作速度快 、带负载能力强 、传输特性好。TTL反相器的电压传输特性:电压传输特性是指输出电压跟随输入电压变化的关系曲线,即UO=f(uI)函数关系。其曲线大致分为四段:AB段(截止区):当UI≤0.6V时,T1工作在深饱和状态,Uces1<0.1V,Vbe2<0.7V,故T2、 T3截止,D、T4均导通, 输出高电平UOH=3.6V。TTL反相器的电压传输特性 BC段(线性区):当0.6V≤UI<1.3V时,0.7V≤Vb2<1.4V,T2开始导通,T3尚未导通。此时T2处于放大状态,其集电极电压Vc2随着UI的增加而下降,使输出电压UO也下降 。CD段(转折区):1.3V≤UI<1.4V,当UI略大于1.3V时, T2 T3均导通, T3进入饱和状态,输出电压UO迅速下降。DE段(饱和区):当UI≥1.4V时,随着UI增加 T1进入倒置工作状态,D截止,T4截止,T2、T3饱和,因而输出低电平UOL=0.3V。

CMOS反相器

CMOS反相器电路由两个增强型MOS场效应管组成,其中V1为NMOS管,称驱动管,V2为PMOS管,称负载管。 NMOS管的栅源开启电压UTN为正值,PMOS管的栅源开启电压是负值,其数值范围在2~5V之间。为了使电路能正常工作,要求电源电压UDD>(UTN+|UTP|)。UDD可在3~18V之间工作,其适用范围较宽。工作原理:当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|>|UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD, 即输出为高电平。当UI=UIH=UDD时,UGS1=UDD>UTN,V1导通,而UGS2=0<|UTP|,因此V2截止。此时UO=UOL≈0,即输出为低电平。 可见,CMOS反相器实现了逻辑非的功能。CMOS反相器的主要特性:在AB段由于V1截止,阻抗很高,所以流过V1和V2的漏电流几乎为0。 在CD段V2截止,阻抗很高,所以流过V1和V2的漏电流也几乎为0。只有在BC段,V1和V2均导通时才有电流iD流过V1和V2,并且在UI=1/2UDD附近,iD最大。

HPM 扰乱效应

基于 CMOS 反相器仿真模型,研究了温度变化对反相器 HPM 扰乱效应的影响。研究表明,反相器所处环境温度越高对 HPM 越敏感,这一结论得到了实验数据的验证,同时又扩充了实验数据所适用的温度范围。研究认为,衬底电阻增大是环境温度升高时反相器 HPM 扰乱效应敏感性增加的主要原因。仿真得到了 HPM 引起的反相器门锁延时特性,通过对温度分布影响的分析,论文指出闩锁延时特性与热边界条件密切相关,器件内部平均温度持续上升导致闩锁效应的大电流通路阻抗增大,从而使得闩锁效应难以继续维持,这一结论为文献中报道的闩锁延时特性提供了微观解释CMOS 反相器的 HPM 扰乱效应机理出发,建立了考虑 HPM 脉宽效应和频率影响的扰乱效应阈值解析模型,并利用仿真结果和实验数据对解析模型进行了验证。研究认为,HPM 导致的过剩载流子注入主导晶体管的电流放大过程,对扰乱效应至关重要。HPM 扰乱脉宽效应可以用反相器寄生晶体管基区过剩载流子随时间的累积效应来解释;而 HPM 频率对扰乱效应的影响则是由于 HPM 频率较高时器件内部交变电场变化太快以致于载流子无法响应,从而影响了 p 型衬底中的注入电荷总量和过剩载流子浓度分布。利用解析模型研究了结构参数 LB对扰乱效应的影响,结果表明 LB较小的 CMOS 反相器对 HPM 更敏感。

参考文献

- ↑ 楔形文字发现后,明明300年没人能看懂,后来为何突然被破译了?,搜狐,2022-10-03

- ↑ 啥是丁头字?圣书字?腓尼基创造了世界最早的字母?还是西奈体?,搜狐,2017-11-21